# Министерство науки и высшего образования РФ Федеральное государственное образовательное учреждение высшего образования

## АМУРСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ (ФГБОУ ВО «АмГУ»)

#### ЭЛЕКТРОТЕХНИКА, ЭЛЕКТРОНИКА И СХЕМОТЕХНИКА

сборник учебно-методических материалов

для направления подготовки 10.03.01 «Информационная безопасность»

Печатается по решению Редакционно-издательского совета энергетического факультета Амурского государственного университета

Составитель: Теличенко Д.А.

Электротехника, электроника и схемотехника: сборник учебно-методических материалов для направления подготовки 10.03.01 — Информационная безопасность. — Благовещенск: Амурский гос. ун-т, 2019.

©Амурский государственный университет, 2019 ©Кафедра автоматизации производственных процессов и электротехники, 2019 ©Теличенко Д.А.

#### Методические указания по освоению дисциплины

Изучение дисциплины студентами должно начинаться со знакомства с рабочей программой и выдаваемыми материалами: методическими пособиями и литературой в электронном формате, а также учебно-методическим комплексом для студентов (далее УМКД, формируемого на основе сборника учебно-методических материалов по дисциплине), в случае необходимости. УМКД это отдельно сформированный документ в электронном варианте содержащий абсолютно все необходимое, включая рабочую программу, методическое рекомендации, пояснения по работе с программным обеспечением и специальными средствами и стендами, задания для самостоятельного выполнения и пр.

Весь материал предварительно размещается на сайте и постоянной доступен, в том числе и в твердой копии на кафедре.

На первом занятии студенты обзорно знакомятся с планом проведения и методикой занятий, узнают конкретные требования к изучению дисциплины, им даются рекомендации, представленные здесь.

Студентам необходимо помнить, что качественна текущая подготовка и проработка материала является залогом успешного освоения предмета.

Студентам рекомендуется за один день до проведения соответствующих занятий познакомиться с планом работ, изучить рассматриваемые вопросы по рекомендуемой литературе и выполнить пункты самостоятельной работы.

После проведения занятий, в этот же день, требуется повторить изученные теоретические положения, выполнить необходимые расчеты и примеры домашних заданий (по факту выдачи). При повторении материала желательно охватывать ранее рассмотренные вопросы; сначала более детально, затем ближе к концу семестра — обзорно.

Такая методика позволяет глубоко проработать все вопросы и не оставляет пробелы в знаниях. В итоге, к окончанию семестра, имеющиеся комплексные знания потребуется лишь освежить в памяти за 2-3 дня до итогового контроля (зачета или экзамена).

Для подготовки к занятиям следует пользоваться литературой, указанной в разделе 10 рабочей программы, в том числе и электронным комплектном материалов. Для общей теоретической подготовки рекомендуется использовать источники п.10.1; при этом вспомогательными источниками п.10.2 необходимо пользоваться по мере необходимости. Для подготовки к практическим, самостоятельным и лабораторным работам рекомендуется использовать пособия, указанные ниже.

Привила проведения аттестации по результатам освоения дисциплины представлены в п.9 рабочей программы. Необходимо помнить при этом, что основой аттестационной оценки является результаты выполнения индивидуальных работ: лабораторных, домашних заданий, РГР – самостоятельно и с полным осознанием выполненных процедур и их результатов.

#### Методические указания к лабораторным работам

Лабораторные работы выполняются по методическим пособиям к имеющимся стендам, см. п.2 и п.3 перечня учебно-методического обеспечения раздела 7 рабочей программы):

- а) Бородянко В.Н., Непопалов В.Н., Шулдяков В.В. Электрические цепи: Методические указания к проведению лабораторных работ на минимодульном стенде «Электрические цепи и основы электроники». Челябинск: Учтех-Профи, 2016;

- а') Бородянко В.Н., Гельман М.В., Непопалов В.Н., Шулдяков В.В. Электрические цепи и основы электроники: Методические указания к проведению лабораторных работ на минимодульной части стенда «Электротехника и основы электроники». Челябинск: Учтех-Профи, 2016;

- б) Гельман М.В., Шулдяков В.В., Верцюх А.С. Основы электроники: Методические указания к проведению лабораторных работ по электронике на минимодульном стенде «Электрические цепи и основы электроники». Челябинск: Учтех-Профи, 2016;

- б') Гельман М.В., Шулдяков В.В., Кучурин А.А., Деев А.С. Электрические цепи и основы электроники: Методические указания к проведению лабораторных работ на минимодульной части стенда «Электротехника и основы электроники». Челябинск: Учтех-Профи, 2016.

- в) Теличенко Д.А., Бушманов А.В. Схемотехника. Лабораторный практикум. Благовещенск: Амурский гос. ун-т, 2006, 93 с.

При этом пособия «а» и «б» являются основными (на них делается ссылка ниже, в таблице распределения работ), а отмеченные «'» – вспомогательные (используемые при проведении компьютеризированных занятий).

Преподавателем до проведения занятий формулируются конкретные требования и порядок выполнения и защиты работ.

Возможно несколько вариантов проведения и защиты работ (конкретный выбор закрепляется за преподавателем, ведущим лабораторные работы и доводится до студентов не позднее второго занятия).

Вне зависимости от варианта проведения лабораторных работ студенты делятся на группы (количество которых определяется по доступными на текущий момент стендам и в соответствии с тем чтобы максимальное число студентов в группе не мешало выполнению работы; рекомендуются группы до 5 человек; рекомендуется группы формировать так что бы уровень подготовки студентов в одной группе был одинаков — определяется, например, по результатам входного тестирования).

Вариант А (базовый). В соответствии с п.6.3 рабочей программы и таблицей, представленной ниже на каждую тему, выделяется отведенное количество часов. Здесь на каждом занятии студенты как выполняют саму работу, так и защищают ее. Данный вариант предполагает: предварительную подготовку заготовок отчетов и выполнение всех заданий непосредственно на самом занятии, одновременно с защитой самой работы. В этом случае вначале занятий преподавателем проверяется подготовка группы к выполнению работы (опрос по теории, просмотр необходимых заготовок; в случае отсутствия подготовки группа или отдельные лица отстраняются от выполнения работы). Затем осуществляется допуск к работе и выполнение работы группой и заполнение заготовки отчетов. В конце занятия, осуществляется защита работы группой или отдельными лицами. Защита предусматривает обсуждение соответствующей теории, ответы на контрольные вопросы, проверку отчетов и выполненных заданий, проверку выводов и глубины усвоения материала в конкретной теме. Предпочтительнее осуществлять индивидуальный допуск и защиту работ.

Вариант Б (усовершенствованный). На всех занятиях отдельно выделяются чередующиеся циклы снятия (выполнения) и защиты работ. При этом в рамках одного занятия (пары – академических 2 часа) проводится только один цикл – снятие или защита работы. В этом случае предусматривается объединение в одно занятие нескольких тем. Порядок допуска и защиты идентичен варианту А.

Вариант В (модифицированный). В данном случае аналогично варианту Б имеются циклы выполнения работ (снятие и защита). Однако здесь в рамках одного занятия отдельные группы снимают работу, другие — защищают. Порядок групп и вида выполняемых ими работ определяется преподавателем.

Примечание: выполнение работ так же предполагает, что для определенной группы студентов возможна выдача дополнительных тем — отмеченных \*; либо наоборот — сокращения объема проводимых исследований для определенного контингента обучающихся.

Вне зависимости от выбранного варианта проведения лабораторных занятий студентам предварительно предлагается самостоятельно ознакомиться с краткой теорией к каж-

дой выполняемой работе и выполнять задания самостоятельно. Это даст необходимую теоретическую основу и облегчит выполнение работ, позволив на занятии уделить большее внимание вопросам, обычно вызывающим наибольшее затруднение. Аналогично так же для каждой темы предполагается проведение трех этапов – допуска, выполнения и зашиты.

Допуск к работе и ее выполнение:

- преподавателем осуществляется допуск к работе, на котором проверяется: знание студентов краткой теории по выполняемой работе; наличие заготовки отчета;

- выясняются вопросы, вызвавшие у студентов затруднения, даются необходимые пояснения по ним;

- даются комментарии по методике проведения экспериментов;

- контролируется выполнение работы каждой бригады и всеми студентами в целом.

Работа считается снятой, если: студенты одной бригады, и каждый в отдельности, выполнили все задания работы, согласно вариантам; зафиксировали снятые данные в заготовку отчета.

При выполнении работ на стендах так же обязательным этапом является после допуска к работе, до подачи питания — демонстрация собранных схем преподавателю для проверки правильности и выполнения условии безопасности.

Защита работы:

- преподавателем, каждому из студентов, выдается произвольный вариант необходимый для выполнения упражнений (если предусмотрено);

- каждый из студентов лично выполняет упражнения (если предусмотрено), согласно выданному на данной работе варианту (в случае если работа не защищается на одном занятии, варианты на упражнения изменяются);

- преподавателем проверяется личный отчет каждого из студентов, задаются вопросы по ходу выполнения работы; задаются контрольные вопросы (список вопросов приведен в лабораторном практикуме к каждой работе).

Работа считается защищенной, если: правильно выполнен отчет по работе; даны корректные ответы на вопросы преподавателя; правильно выполнены упражнения (если предусмотрены).

Представляемый отчет (после успешной защиты работы отчет сдается преподавателю и сохраняется до успешной сдачи студентом экзамена) должен удовлетворять следующим требованиям:

- отчет выполняется на одной стороне белого листа формата А4 в рукописной или печатной форме, в варианте возможном для прочтения (почерк, шрифт, размер, интервал);

- титульный лист должен содержать следующие сведения: название предмета; тему работы, с ее порядковым номером; фамилию студента, выполнившего работу с указанием номера группы и вариантов (личного и на бригаду); фамилию преподавателя, осуществляющего прием работы; дату снятия и защиты (дата защиты заполняется преподавателем лично).

- основная часть работы должна содержать следующие сведения: краткую теорию; цель работы; элементы, приборы и инструменты, используемые в работе; ход работы с необходимыми рисунками, схемами, таблицами, формулами и пояснениями.

В случае если студент не снял или не защитил работу, он может приступать к следующей работе. Ликвидировать возникшую задолженность можно на оставшемся времени после проведения очередной лабораторной работы или на дополнительных занятиях. Если ликвидировать задолженность по лабораторным работам в течение семестра не удается, студент является на экзамен с отчетами по несданным работам, где ему до ответа на экзаменационные вопросы дается возможность защитить каждую работу.

План проведения занятий с указанием последовательности изучаемых тем, объема часов, представлен в виде таблиц. При этом в последней колонке представлены ссылки на номера работ лабораторных пособий. Проведение работ предполагает гибкое распределе-

ние тем, с учетом успехов студентов при освоении дисциплины, и как было указано выше может гибко меняться как в одну сторону, так и в другую — это не уменьшит объема полученных знаний, так как соответствующие темы отрабатываются на лекциях и практиках.

#### Методические указания к практическим работам

Предварительно студенты знакомятся со списком всех изучаемых тем, рассматриваемых на практических занятиях. Характер вопросов, прорабатываемых здесь, связан с лекционным курсом и графиком самостоятельной работы. Большая часть времени уделяется решению конкретных задач (аналогичные по тематике задачи использованы в качестве экзаменационного вопроса). Эти же задачи частично входят в домашние задания (РГР).

Задачи решаются студентами самостоятельно. При этом один из студентов вызывается к доске, решает поставленную задачу. Преподавателем контролируется не только правильность решения, но и даются: практические рекомендации по выполнению подобных заданий, применимость рассматриваемых тем к практике, а также предлагается другим студентам предложить альтернативные способы решения. Каждому вышедшему к доске, а также студентам, принявшим участие в обсуждении, выставляется оценка.

План проведения практических занятий, включая темы, объем часов представлен выше.

Методическое обеспечение данного вида работ представлено в приложении Б.

#### Методические указания по самостоятельной работе

Самостоятельная работа предполагает проработку вопросов теории и практики в соответствии с учебной программой.

Основная часть работы здесь связана с подготовкой к лабораторным и практическим работам – см выше, а также выполнении РГР.

Индивидуальные практические задания (РГР) предусмотрены только для главы 3 «Схемотехника». Сами задания изложены в формируемом отдельно УМКД или базируются на имеющемся в свободном доступе методическом обеспечении (представлены так же в приложении Б). Все задания РГР выполняются письменно персонально каждым студентов и оформляются в соответствии с действующими стандартами АмГУ на листах белой бумаги формата А4 (рукописным или печатным способом) в варианте возможным для прочтения.

В общем случае РГР состоит из следующих разделов: титульный лист (со всеми данными касающимися выполнившего работу студента, его варианта задания и пр.); задания к работе; решение соответствующих заданий (включая все необходимые выкладки и пояснения по их решениям, расчеты, доказательства и построения, графические иллюстрации, таблицы и пр.).

Защита РГР предполагает индивидуальную беседу со студентом, где выясняется уровень освоения материала, аутентичность работы с точки зрения авторства. Защита работы проводится в рамках итоговой аттестации по дисциплине либо на консультациях перед экзаменом, либо на самом экзамене.

Подготовка к защите и выполнение работы предполагает выполнение заданий осуществляемых в рамках практических работ по главе 3 (см. выше) и содержит только те заданий, которые студенты выполняют на практиках; аналогичные задания имеются в экзаменационных билетах.

### УЧЕБНО-МЕТОДИЧЕСКОЕ ОБЕСПЕЧЕНИЕ ЛАБОРАТОРНЫХ РАБОТ

#### ЛАБОРАТОРНАЯ РАБОТА № 1

#### ИЗУЧЕНИЕ ЛОГИЧЕСКИХ СХЕМ И ФУНКЦИЙ

#### Цель работы.

- 1. Исследование базовых логических элементов.

- 2. Реализация логических функций при помощи логических элементов.

- 3. Синтез логических схем.

#### Приборы и элементы.

Логический преобразователь (панель «Instruments/Logic Converter»).

Генератор слов (панель «Instruments/Word Generator»).

Вольтметр (панель «Indicators/Voltmeter»).

Логические пробники (панель «Indicators/Red probe»).

Источник напряжения + 5 В (панель «Basic/Pull-Up Resistor»).

Земля (панель «Sources/Ground»).

Двухпозиционные переключатели (панель «Basic/Switch»).

Двухвходовые элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ (панель «Logic Gates/2-Input AND, NAND, OR, NOR Gates»).

Микросхемы различных серий (панель «Logic Gates/»).

#### Краткие теоретические сведения

Любые цифровые микросхемы современных вычислительных машин строятся на основе простейших логических элементов «И», «ИЛИ», «НЕ» и их комбинаций. В настоящее время используется несколько технологий построения логических элементов:

транзисторно-транзисторная логика (ТТЛ, TTL);

логика на основе комплементарных МОП транзисторов (КМОП, СМОЅ);

логика на основе сочетания комплементарных МОП и биполярных транзисторов (БиКМОП);

эмиттерно-связанная логика (ЭСЛ) и т.д.

Прежде чем приступить к изучению базовых логических элементов, введем основные понятия булевой алгебры, или алгебры логики, на которой базируется все теоретическое обоснование работы цифровых устройств.

#### 1. Основные определения и аксиомы алгебры логики

Переменные, рассматриваемые в алгебре логики, принимают только два значения – «0» или «1». Чаще всего сами переменные обозначаются латинскими буквами: либо малыми (x, y, z, ...), либо большими (A, B, C,...).

<u>Примечание.</u> Физически самым простым устройством, моделирующим поведение любой булевой переменной, является двухпозиционный переключатель. У него за логический сигнал «1» принимается положение «включено», а за сигнал — «0» положение «выключено». Поэтому самой простой схемой для изучения логических функций и выражений является электрическая, состоящая из исследуемого элемента или элементов, источников питания, заземления и устройств, моделирующих задание уровней логических сигналов (в простейшем случае ими являются переключатели). Причем в данном случае важно подчеркнуть неразрывную связь между физическим сигналом (ток или напряжение) и логическим сигналом: за логический сигнал «0» и «1» принимаются определенные уровни физических сигналов (чаще всего за логический «0» принимается сигнал по напряжению в 0 В, а за уровень логической «1» +5 В).

Перечислим основные операции и аксиомы алгебры логики.

Основные операции алгебры логики:

отношение эквивалентности, обозначаемое знаком «=»;

операция логического сложения (дизъюнкция), обозначаемая знаком  $\langle\!\langle \, \, \, \rangle\!\rangle$  или  $\langle\!\langle + \, \, \, \, \, \rangle$ ;

операция логического умножения (конъюнкция), обозначаемая знаком  $(\land \land)$  или  $(\bullet)$ ;

операция отрицания (инверсии), обозначаемая надчеркиванием или апострофом «'». Основные аксиомы булевой алгебры:

$$\begin{cases}

\overline{0} = 1, \\

T = 0.

\end{cases}

\begin{cases}

0 \lor 0 = 0 + 0 = 0, \\

1 \lor 0 = 1 + 0 = 1, \\

1 \lor 1 = 1 + 1 = 1.

\end{cases}

\begin{cases}

0 \land 0 = 0 \cdot 0 = 0, \\

0 \land 1 = 0 \cdot 1 = 0, \\

1 \land 1 = 1 \cdot 1 = 1.

\end{cases}$$

(1)

#### 2. Логические выражения

Из логических переменных с помощью базовых логических операций можно составить <u>логическое выражение</u>. Логические выражения связывают значение логической функции со значениями логических переменных.

Логическое выражение является одним из способов описания цифрового устройства.

Запись логических выражений обычно осуществляют в конъюнктивной или дизъюнктивной нормальных формах. В дизъюнктивной форме логические выражения записываются как логическая сумма логических произведений, в конъюнктивной форме – как логическое произведение логических сумм.

#### 3. Логические тождества

При преобразованиях логических выражений используются следующие логические тождества:

$$\overline{\overline{x}} = x; \quad x \lor 1 = 1; \quad x \lor 0 = x; \quad x \cdot 1 = x; \quad x \cdot 0 = 0;$$

$$x \lor x = x; \quad x \cdot x = x; \quad x \lor x \cdot y = x;$$

$$xy \lor x\overline{y} = x; \quad (x \lor y)(x \lor \overline{y}) = x; \quad x \lor \overline{x}y = x \lor y;$$

$$\overline{xy} = \overline{x} \lor \overline{y}; \quad \overline{x} \lor \overline{y} = \overline{xy}.$$

(2)

#### 4. Логические функции

Любое логическое выражение, составленное из n переменных  $x_n$ ,  $x_{n-1}$ ,... $x_I$ , с помощью конечного числа операций алгебры логики, можно рассматривать как некоторую функцию n переменных. Такую функцию называют логической. В соответствии с аксиомами алгебры логики такая функция может принимать (в зависимости от значения логических переменных, входящих в нее)

значение «0» или «1». Функция n логических переменных может быть определена для  $2^n$  значений переменных, соответствующих всем возможным значениям n-разрядных двоичных чисел. Основной интерес представляют следующие базовые логические функции двух переменных x и y:

$$f 1(x, y) = x \cdot y$$

– логическое умножение (конъюнкция), (3)

$$f2(x, y) = x \vee y$$

– логическое сложение (дизъюнкция), (4)

$$f3(x, y) = x \cdot y$$

— логическое умножение с инверсией, (5)

$$f4(x,y) = \overline{x \vee y}$$

— логическое сложение с инверсией, (6)

$$f 5(x, y) = x \oplus y = x\overline{y} \vee \overline{x}\overline{y}$$

– суммирование по модулю 2, (7)

$$f 6(x, y) = \overline{x \oplus y} = xy \vee \overline{xy}$$

– равнозначность. (8)

#### 5. Логические схемы

Физическое устройство, реализующее одну из операций алгебры логики или простейшую логическую функцию, называется <u>логическим элементом</u>. Схема, составленная из конечного числа логических элементов по определенным правилам, называется логической схемой. Логическая схема, наряду с логическим выражением, является одним из способов задания цифровых элементов.

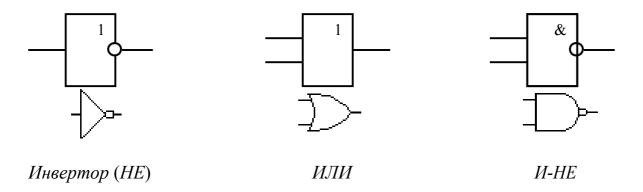

Условное обозначение основных логических элементов, принятых в нашей стране и за рубежом, приведено на рис. 1.

Рис. 1. Обозначение логических элементов.

<u>Примечание.</u> Количество входов в приведенных элементах может быть произвольным; на операцию инвертирования указывает кружок на выходном сигнале.

На рис. 1 в первом ряду приведено обозначение, принятое в нашей стране, во втором ряду, обозначение, принятое за рубежом.

#### 6. Таблица истинности

Поскольку область определения любой логической функции n переменных конечна ( $2^n$  значений), то такая функция может быть задана таблицей значений  $f(v_i)$ , которые она принимает в точках  $v_i$ , где  $i = 0, 1... 2^n$ -1. Такие таблицы называют таблицами истинности. В табл. 1 представлены таблицы истинности, задающие указанные выше функции (3) – (8).

*Таблица 1*. Произвольная таблица истинности

| Nº |   | ения<br>енных | Функции |    |    |    |    |    |

|----|---|---------------|---------|----|----|----|----|----|

|    | X | y             | f1      | f2 | f3 | f4 | f5 | f6 |

| 1  | 0 | 0             | 0       | 0  | 1  | 1  | 0  | 1  |

| 2  | 0 | 1             | 0       | 1  | 1  | 0  | 1  | 0  |

| 3  | 1 | 0             | 0       | 1  | 1  | 0  | 1  | 0  |

| 4  | 1 | 1             | 1       | 1  | 0  | 0  | 0  | 1  |

В общем случае таблица истинности должна содержать все возможные комбинации логических переменных, входящих в логическое выражение (в случае табл. 1 это комиции логических переменных x и y), и значения логического выражения, соответствующие каждой комбинации логических переменных

Таблица истинности является третьим способом задания цифровых элементов. Необходимо отметить, что все три способа задания (с помощью логических выражений, логических схем и таблиц истинности) являются однозначными и в равной мере взаимозаменяемыми. Так, по логическому выражению можно составить схему и записать таблицу истинности и наоборот.

#### 7. Получение логических выражений

Целью преобразования сложных логических выражений (а также получения по экспериментальной таблице истинности логического выражения, описывающего данную логическую зависимость) является компактная форма записи, которая в полной мере описывает данную логическую зависимость от любого числа переменных. Операции с логическими выражениями намного удобней, чем с таблицами истинности и со схемами.

Самый простой способ получения логических выражений — это анализ таблицы истинности. Для наглядности рассмотрим пример: пусть требуется найти логическое выражение для функции fm трех переменных X, Y, Z, описываемых табл. 2.

Таблица 2. Таблица истинности функции *fm*

| Nº | X | Y | Z | fm |

|----|---|---|---|----|

| 1  | 0 | 0 | 0 | 0  |

| 2  | 0 | 0 | 1 | 0  |

| 3  | 0 | 1 | 0 | 0  |

| 4  | 0 | 1 | 1 | 1  |

| 5  | 1 | 0 | 0 | 0  |

| 6  | 1 | 0 | 1 | 1  |

| 7  | 1 | 1 | 0 | 1  |

| 8  | 1 | 1 | 1 | 1  |

Из правил записи логических выражений следует, что искомую зависимость можно получить в двух видах (конъюнктивной или дизъюнктивной нормальных формах — пункт 2). Чаще всего на практике применяется дизъюнктивно нормальная форма записи логической функции.

Дизъюнктивно нормальная форма записи представляет собой дизъюнкцию (логическое сложение) элементарных конъюнкций (произведение всех логических переменных, в нашем случае – это три переменные X, Y, Z).

Для записи логического выражения в дизъюнктивно нормальной форме выберем из таблицы истинности 2 строки, в которых функция fm принимает значение «1». Это строки 4, 6, 7, 8. Таким образом, элементов нашей дизъюнк-

ции будет 4 (всего слагаемых). Каждое слагаемое — это элементарная конъюнкция. В каждую же элементарную конъюнкцию (произведение), как уже было сказано, должны войти все логические переменные данной строки (в нашем случае *X, Y, Z*). При этом если соответствующий элемент (X, Y или Z) имеет для данной строки значение «1», то он входит в элементарную конъюнкцию (произведение) в обычном виде, если же он равен «0», то необходимо взять его отрицание. Так, для каждой строки имеем элементарную конъюнкцию (произведение) в следующем виде:

$ar{X} \cdot Y \cdot Z$  для строки 4;  $X \cdot ar{Y} \cdot Z$  для строки 6;  $X \cdot Y \cdot ar{Z}$  для строки 7;  $X \cdot Y \cdot Z$  для строки 8.

Искомой формой записи данного логического выражения в дизъюнктивно нормальной форме является дизъюнкция (сложение) полученных выше 4 конъюнкций:

$$fm = \overline{X}YZ \vee X\overline{Y}Z \vee XY\overline{Z} \vee XYZ . \tag{9}$$

По данной логической функции можно записать таблицу истинности, идентичную табл. 2. Для этого необходимо в логическую функцию подставлять все возможные комбинации логических переменных X, Y, Z (всего таких значений  $2^3$ ) и на каждой подстановке, пользуясь аксиомами алгебры логики, вычислять функцию fm.

Необходимо отметить, что данный способ получения логических выражений не самый рациональный. Полученная логическая функция, хоть и содержит исчерпывающую информацию о выбранной комбинации логических переменных, тем не менее поддается еще упрощению с помощью выражений (2).

Другим способом составления упрощенного выражения по таблице истинности является составление карт Карно. Такой способ в данной работе не рассматривается по двум причинам:

во-первых, наглядность его минимальна при достаточно большой сложности построения самих карт Карно, что вызывает большие трудности у студентов, особенно в начале изучения цифровой техники;

во-вторых, методика построения карт Карно хорошо описана в соответствующей литературе.

#### Порядок работы

#### Задание 1. Исследование логической функции «И»

Задание уровней логических сигналов.

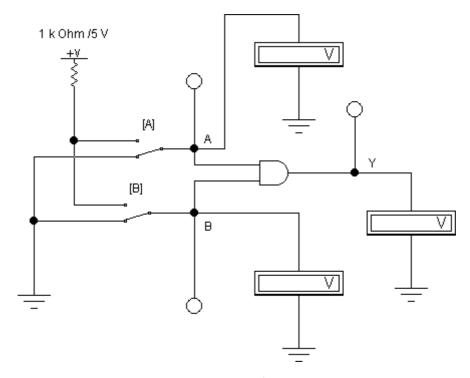

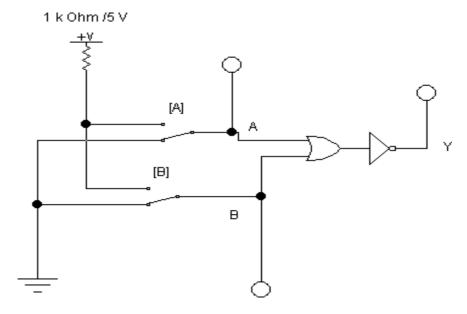

Создайте схему, изображенную на рис. 2.

Рис. 2. Логическая функция «И».

В этой схеме два двухпозиционных переключателя «А» и «В» подают на входы логической схемы «И» уровни логических сигналов: «0» (контакт переключателя в нижнем положении) или «1» (контакт переключателя в верхнем положении). В физическом плане это соответствует подаче напряжения от источника (+ 5 В) на логический элемент. Уровень физического сигнала на входе или выходе логического элемента можно измерить с помощью вольтметра (в

данном случае «0» В или «+5» В), а уровень <u>логического сигнала</u> – с помощью логических пробников, которые информируют о наличии на измеряемой линии сигнала вообще (если сигнал есть, то пробник загорается).

Включите схему (тумблером, находящимся в правом верхнем углу окна программы). Установите положения ключей в соответствии с табл. 3. Результаты замеров (логических и физических сигналов) занесите в табл. 3.

*Таблица 3*. Задание уровней логических сигналов

| Положение переключателей |         |                         | Сигналы на входах и выходе |   |                  |   |   |

|--------------------------|---------|-------------------------|----------------------------|---|------------------|---|---|

| <b>«A»</b>               | «B»     | Логические<br>(0 или 1) |                            |   | Физические,<br>В |   |   |

|                          |         | A                       | В                          | Y | A                | В | Y |

| Нижнее                   | Нижнее  |                         |                            |   |                  |   |   |

| Нижнее                   | Верхнее |                         |                            |   |                  |   |   |

| Верхнее                  | Нижнее  |                         |                            |   |                  |   |   |

| Верхнее                  | Верхнее |                         |                            |   |                  |   |   |

<u>Примечание.</u> Прежде чем начать работу с переключателями удобно каждому переключателю присвоить букву, при нажатии которой он включается/выключается. Это можно сделать до начала работы схемы, дважды щелкнув на переключатель и на закладке «Value» присвоив ему уникальную кнопку.

Экспериментальное получение таблицы истинности элемента «И».

Подайте на входы схемы (рис. 2) все возможные комбинации уровней сигналов «А» и «В» и для каждой комбинации зафиксируйте уровень выходного сигнала «Y». Заполните таблицу истинности исследуемой логической схемы «И» (табл. 4).

Таблица 4. Таблица истинности логического элемента «И»

| Входы |   | Выход |

|-------|---|-------|

| A     | В | Y     |

|       |   |       |

|       |   |       |

|       |   |       |

|       |   |       |

Получение аналитического выражения для функции.

По табл. 4 составьте аналитическое выражение функции элемента «И» и занесите его себе в отчет. Для этого можно воспользоваться одним из двух способов получения логических выражений по таблице истинности, изложенных в кратких теоретических данных лабораторной работы.

#### Задание 2. Исследование логической функции «И-НЕ»

Экспериментальное получение таблицы истинности логического элемента «И-НЕ», составленного из элементов «И» и «НЕ».

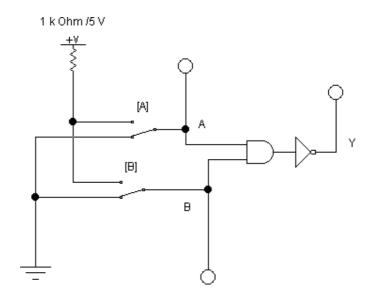

Соберите схему, изображенную на рис. 3.

Рис. 3. Логическая функция «И-НЕ».

Включите схему. Подайте на входы схемы все возможные комбинации уровней входных сигналов и, наблюдая уровни сигналов на входах и выходе с помощью логических пробников, заполните таблицу истинности логической схемы «И-НЕ» (табл. 5).

*Таблица 5*. Таблица истинности элемента «И-НЕ» (составного)

| Входы |   | Выход        |

|-------|---|--------------|

| A     | В | $\mathbf{Y}$ |

| 0     | 0 |              |

| 0     | 1 |              |

| 1     | 0 |              |

| 1     | 1 |              |

Экспериментальное получение таблицы истинности логического элемента «И-НЕ».

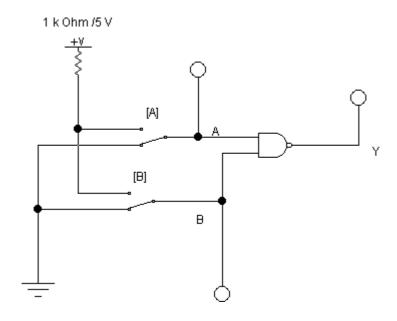

Соберите схему, изображенную на рис. 4.

Рис. 4. Логическая функция «И-НЕ».

Включите схему. Подайте на входы схемы все возможные комбинации уровней входных сигналов и, наблюдая уровни сигналов на входах и выходе с помощью логических пробников, заполните таблицу истинности логической схемы «И-НЕ» (табл. 6).

*Таблица 6*. Таблица истинности элемента «И-НЕ»

| Входы |   | Выход |

|-------|---|-------|

| A     | В | Y     |

| 0     | 0 |       |

| 0     | 1 |       |

| 1     | 0 |       |

| 1     | 1 |       |

Сравните между собой табл. 5 и 6 и сделайте соответствующие выводы.

#### Задание 3. Исследование логической функции «ИЛИ»

Экспериментальное получение таблицы истинности логического элемента «ИЛИ».

Включите схему. Подайте на входы схемы все возможные комбинации уровней входных сигналов и, наблюдая уровни сигналов на входах и выходе с

помощью логических пробников, заполните таблицу истинности логической схемы «ИЛИ» (табл. 7).

*Таблица 7.* Таблица истинности элемента «ИЛИ»

| Входы |   | Выход |

|-------|---|-------|

| A     | В | Y     |

| 0     | 0 |       |

| 0     | 1 |       |

| 1     | 0 |       |

| 1     | 1 |       |

Получение аналитического выражения для функции.

По табл. 7 составьте аналитическое выражение функции «ИЛИ» и занесите его в отчет. Для этого можно воспользоваться одним из двух способов получения логических выражений по таблице истинности, изложенных в кратких теоретических данных данной лабораторной работы.

#### Задание 4. Исследование логической функции «ИЛИ-НЕ»

Экспериментальное получение таблицы истинности логического элемента «ИЛИ-НЕ», составленного из элементов «ИЛИ» и «НЕ».

Соберите схему, изображенную на рис. 6.

Рис. 6. Логическая функция «ИЛИ-НЕ».

Включите схему. Подайте на входы схемы все возможные комбинации уровней входных сигналов и, наблюдая уровни сигналов на входах и выходе с помощью логических пробников, заполните таблицу истинности логической

*Таблица 8*. Таблица истинности элемента «ИЛИ-НЕ» (составного)

| Входы |   | Выход |

|-------|---|-------|

| A     | В | Y     |

| 0     | 0 |       |

| 0     | 1 |       |

| 1     | 0 |       |

| 1     | 1 |       |

Экспериментальное получение таблицы истинности логического элемента «ИЛИ-НЕ».

Соберите схему, изображенную на рис. 7.

Включите схему. Подайте на входы схемы все возможные комбинации уровней входных сигналов и, наблюдая уровни сигналов на входах и выходе с помощью логических пробников, заполните таблицу истинности логической схемы «ИЛИ-НЕ» (табл. 9).

*Таблица 9*. Таблица истинности элемента «ИЛИ-НЕ»

| Входы |   | Выход |

|-------|---|-------|

| Α     | В | Y     |

| 0     | 0 |       |

| 0     | 1 |       |

| 1     | 0 |       |

| 1     | 1 |       |

Сравните табл. 8 и 9 между собой и сделайте соответствующие выводы.

### Задание 5. Исследование логических схем с помощью генератора слов

Анализ различных логических функций иногда удобно проводить с помощью микросхем, реализующих различные логические элементы. Кроме того, использование микросхем (в отличие от расширенного представления логических функций, рассматриваемого в предыдущих заданиях) бывает необходимо на стадии проектирования сложных систем, когда в руках современного инженера зачастую имеется набор из различных, законченных модулей, реализующих вполне определенные функции.

Отдавая дань доступности и широкому распространению англоязычных микросхем, а также их аналогов, изготовленных по западным стандартам (в том числе и современные российские разработки), в данной работе мы рассматриваем микросхемы как раз западного стандарта.

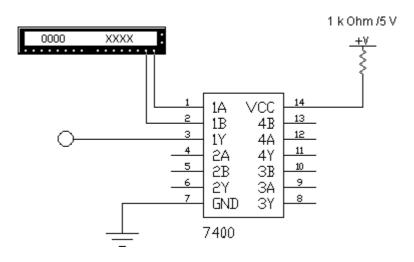

Помимо того, для дальнейшего рассмотрения цифровой техники удобно вместо коммутирующих выключателей (задающих уровни логических сигналов) в некоторых случаях использовать «генератор слов» (прибор, предназначенный для выработки последовательности логических сигналов на своих выходах, причем данную последовательность пользователь имеет возможность задавать самостоятельно). Использованию модульных микросхем и «генератора слов» посвящено следующее задание.

Исследование модульных микросхем различных типов.

Выбор исследуемой микросхемы производится по номеру варианта, присвоенному студенту преподавателем. Типы микросхем в соответствии с вариантом задания приведены в табл. 10.

Таблица 10.

Варианты задания исследуемой микросхемы

| Вариант задания | Тип микросхемы |  |

|-----------------|----------------|--|

| 1               | AND/7408       |  |

| 2               | AND/7421       |  |

| 3               | AND/7411       |  |

| 4               | NOR/7402       |  |

| 5               | NOR/7427       |  |

| 6               | NOR/7428       |  |

| 7               | NOR/7433       |  |

| 8               | OR/7432        |  |

| 9               | XOR/7486       |  |

| 10              | XNOR/74266     |  |

<u>Примечание.</u> Данные микросхемы в общем случае могут содержать несколько независимых друг от друга логических элементов (но одного типа: например, 3 логических элемента «И» – «AND»), причем у каждого логическо-

го элемента может быть и несколько входов (1, 2, 3 или 4).

После выбора соответствующей микросхемы нужно собрать схему для ее изучения. В общем случае она должна содержать: источник напряжения, заземление (земля), необходимое количество логических пробников и генератор слов.

Пример собранной схемы для исследования микросхемы NOR/7400 приведен на рис. 8.

Рис. 8. Исследование микросхемы NOR/7400.

<u>Примечание.</u> Для дальнейшего исследования необходимо <u>принимать во</u> внимание только входы/выходы одного логического элемента на данной микросхеме (на рис. 8 используется первый логический элемент).

В отчете по данному пункту необходимо заполнить табл. 11, дающую исчерпывающую информацию об используемой микросхеме.

<u>Примечание.</u> Исчерпывающую информацию об используемой микросхеме можно получить в справке (выделите интересующий вас элемент и щелкните на знак вопроса).

Экспериментальное получение таблицы истинности микросхемы.

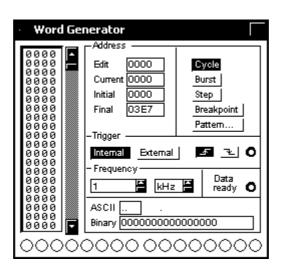

Для дальнейшего изучения микросхемы необходимо использовать «генератор» слов (предполагается, что при выполнении задания 5.2. была собрана схема для изучения, аналогичная рис. 8). Общий вид открытого окна свойств «генератора» показан на рис. 9. Для открытия данного окна необходимо дважды щелкнуть мышью на изображении генератора слов.

*Таблица 11*. Информация о микросхеме

| Тип микросхемы (полное обозначение по варианту задания)    |

|------------------------------------------------------------|

| Тип базисных элементов (логических функций)                |

| Число базисных элементов в микросхеме (всего)              |

| Число исследуемых базисных элементов в микросхеме          |

| Обозначение выводов микросхемы, используемых для подключе- |

| ния источника питания (номера и название)                  |

| Обозначения выводов микросхемы, используемых для подключе- |

| ния заземления (номера и название)                         |

| Обозначение используемых входов (номера и название)        |

| Обозначение используемых выводов (номера и название)       |

Рис. 9. Генератор слов.

Окно свойств может быть условно разбито на ряд частей.

<u>В левой части</u>, в прокручивающимся окне, отображаются слова (набор логических последовательностей), формируемые «генератором слов» в 16-ричной системе исчисления (данные последовательности могут быть изменены пользователем).

<u>В правой части</u> окна свойств находится ряд областей («Address», «Trigger», «Data ready»,), несущих техническую информацию. Из этих областей мы будем пользоваться только кнопками «Cycle» и «Step», переводящие генератор слов в цикловой (заданные пользователем слова прокручиваются автоматиче-

ски) и пошаговый режимы работы (каждая следующая последовательность, вырабатываемая «генератором слов», вызывается нажатием кнопки «Step»).

<u>В правой нижней части</u> окна свойств находятся поля «ASCII», «Binary и ряд, состоящий из логических пробников. Поле «Binary» (изменяемое) и ряд пробников, (функционирующих только в режиме «Работа»), имеют одинаковую информационную сущность. Они отображают генерируемые последовательности слов в двоичном коде.

Отметим также, что часто бывает удобнее задавать последовательность слов именно в поле «Віпагу», которое связано (изменение его вызывает изменение другого поля) и с прокручивающимся списком генерируемых слов, находящимся в левой части и рассмотренным ранее.

Для выполнения работы запрограммируйте «генератор слов» так, чтобы на его выходе получит последовательно следующие комбинаций: 00, 01, 10, 11 (необходимо помнить: несмотря на то, что в анализируемых микросхемах количество базисных логических элементов и входов на каждом элементе множество, мы исследуем только два входа одного базисного логического элемента). Затем переведите генератор в режим пошаговой работы нажатием кнопки «Step» в окне свойств генератора. Каждое нажатие кнопки «Step» вызывает переход к очередному слову заданной последовательности, которое подается на выход генератора. Последовательно подавая на микросхему слова из заданной последовательности, заполните таблицу истинности элемента вашего базисного элемента (табл. 12).

Таблица 12.

Таблица истинности исследуемой микросхемы

| Входы  |        | Выход        |

|--------|--------|--------------|

| первый | второй | $\mathbf{Y}$ |

| 0      | 0      |              |

| 0      | 1      |              |

| 1      | 0      |              |

| 1      | 1      |              |

<u>Указание.</u> Для повторения запрограммированной комбинации слов можно выключить и включить схему заново, тогда последовательности, заданные в «генераторе слов», будут изменяться начиная с первой.

## Задание 6. Реализация логической функции 3-х и большего числа переменных

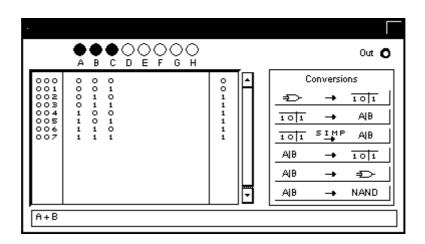

В заключение изучения базовых логических схем и функций приведем задание, иллюстрирующее возможности «Electronic Workbench» в такой непростой и трудно формализуемой задаче как синтез логических схем и функций. Все предыдущие задания опирались в основном на моделирование уже существующих логических функций и изучение их свойств. Выполнив же это задание, студенты смогут автоматически реализовывать любую логическую функцию, заданную булевым выражением в различных базисах, получать таблицы истинности логических выражений и т. п. Все перечисленные процедуры можно реализовать с помощью инструмента «Logic Converter». Общий вид окна свойств «Logic Converter» показан на рис. 10.

Puc. 10. «Logic Converter».

Напомним, что окно свойств вызывается двойным нажатием на изображении инструмента. Рассмотрим окно свойств подробнее.

Здесь <u>в верхней части</u> под буквами A, B,...,Н находятся индикаторы, активизируемые путем нажатия на них. На рис. 10 активизированы три индикатора – A, B, C. Подразумевается, что в дальнейшем мы будем оперировать ло-

гической функцией, состоящей из трех переменных — A, B, C. Данный выбор вызывает появление всех возможных комбинаций этих переменных (строки таблицы, изображенной на рис. 10, начиная с нулевой и заканчивая седьмой). В правой части полученной таблицы истинности, в отдельном столбце, по умолчанию присвоены «0» выходной переменной. Пользователь, изменяя значения выхода анализируемой логической функции, тем самым полностью задает таблицу истинности.

<u>В самом нижнем окне</u> находится поле ввода/вывода логической функции (поле является <u>выводящим</u>, если пользователь сам задал таблицу истинности, а затем путем нажатия на соответствующую функциональную кнопку потребовал формирования логической функции; и поле является <u>вводящим</u>, если пользователь предварительно сам задал логическую функцию, а затем путем нажатия на соответствующую функциональную кнопку потребовал формирования таблицы истинности).

<u>В правой части</u> окна свойств находятся соответствующие функциональные кнопки (панель «Conversion»).

- 1) получение таблицы истинности для произвольной логической схемы, подсоединенной к входам и выходам «Logic Converter»;

- 2) АВ получение по таблице истинности логической функции (не упрощенной);

- 3) получение по таблице истинности упрощенной логической функции (аналогичная функция получается путем использования для анализа таблицы истинности карт Карно);

- 4) получение по логической функции таблицы истинности;

5) — → — — — — — получение по логической функции схемы, реализованной в произвольном базисе;

6) — МАНО — получение по таблице истинности логической функции реализованной в базисе «И-НЕ».

Синтез схемы, реализующей заданную функцию при помощи логического преобразователя.

Для получения схемы, реализующей функцию, описываемую логическим выражением f (задается преподавателем), можно воспользоваться логическим преобразователем. Варианты заданий логических выражений приведены в табл. 13 (здесь апостроф указывает на операцию инвертирования).

Tаблица 13. Варианты задания логического выражения f

| Вариант задания | Логическое выражение $m{f}$ |

|-----------------|-----------------------------|

| 1               | A+B*C                       |

| 2               | C+A*B                       |

| 3               | A*B*C                       |

| 4               | A'+B+C                      |

| 5               | A+B°C                       |

| 6               | C*B'+A                      |

| 7               | A'+B'+C'                    |

| 8               | C'+A'*B                     |

| 9               | A'+B'+C                     |

| 10              | B+C*A'                      |

Проделайте с анализируемым логическим выражением следующие действия:

- 1) вызовите логический преобразователь;

- 2) введите в нижнее окно панели преобразователя логическое выражение с клавиатуры (операции ИЛИ соответствует знак «+», инверсия обозначается апострофом, логическая операция умножения не вводится: например, AB=A\*B);

- 3) для реализации схемы на элементах «И-НЕ» нажмите соответствующую функциональную кнопку на панели логического преобразователя, занесите полученную схему в отчет, удалите полученную схему;

- 4) для простой реализации схемы на произвольных элементах нажмите соответствующую функциональную кнопку на панели логического преобразователя, занесите полученную схему в отчет, удалите полученную схему;

- 5) для получения таблицы истинности заданной логической функции нажмите соответствующую функциональную кнопку на панели логического преобразователя, занесите полученную таблицу истинности в отчет.

Синтез логической функции, реализующей заданную таблицу истинности при помощи логического преобразователя.

Для получения функции, реализующей таблицу истинности, необходимо воспользоваться таблицей истинности, полученной в предыдущем пункте. Для этого проделайте следующее:

- 1) удалите с нижней строки логического преобразователя логическую функцию;

- 2) очистите таблицу истинности преобразователя, нажав на его верхнюю функциональную кнопку;

- 3) выберите в поле таблицы истинности количество используемых логических переменных (в нашем случае их 3) путем нажатия на соответствующие индикаторы;

- 4) в правой колонке полученной таблицы истинности задайте значение искомой логической функции в соответствии с каждой строкой;

- 5) для получения неупрощенной логической функции нажмите соответствующую функциональную кнопку на панели логического преобразователя, занесите в отчет полученную функцию;

- 6) для получения упрошенной логической функции нажмите соответствующую функциональную кнопку на панели логического преобразователя, запишите упрощенную логическую функцию;

- 7) удостоверьтесь, что упрощенные модели совпадают с заданными в начале моделями;

- 8) удостоверьтесь, что упрощенная функция может быть получена из неупрощенной (проделайте операции упрощения).

#### Контрольные вопросы

- 1. Дайте определение логического сигнала.

- 2. Дайте определение логической переменной.

- 3. Дайте определение логической функции.

- 4. Какие значения могут принимать булевы переменные?

- 5. Приведите основные логические тождества.

- 6. Что может быть принято за уровни логических сигналов?

- 7. Подумайте, почему в технике за уровень логического нуля часто принимают физический сигнал (например, по току), отличный от нуля?

- 8. Как может быть получена логическая функция?

- 9. Чем в физическом смысле отличается работа схемы составленной по упрощенной логической функции, от неупрощенной?

- 10. Сколько различных комбинаций сигналов надо подать на схему, имеющую 4 входа, для составления таблицы истинности?

- 11. Какой сигнал должен быть подан на неиспользуемые входы элемента «И-НЕ», имеющего 5 входов, если требуется реализовать ту же логическую функцию, но на 3 входа?

- 12. Какой сигнал должен быть подан на неиспользуемые входы элемента «ИЛИ», имеющего 5 входов, если требуется реализовать ту же логическую функцию, но на 4 входа?

- 13. Какой сигнал нужно подать на неиспользуемые входы элемента «И», имеющего 2 входа, для реализации на его базе инвертора на один входной сигнал?

- 14. Какой логической функцией можно описать систему пуска трехфазного двигателя, если двигатель может быть запущен, когда три дат-

#### чика подтверждают наличие фазных напряжений?

#### Упражнения

#### 1. Получение логических функций

По заданной таблице истинности (табл. 14) получите логическую функцию.

*Таблица 14*. Варианты таблицы истинности

| Значения логических<br>переменных<br>(для всех вариантов) |   |   | Варианты задания |                                                       |   |   |   |   |   |   |   |    |   |

|-----------------------------------------------------------|---|---|------------------|-------------------------------------------------------|---|---|---|---|---|---|---|----|---|

|                                                           |   |   | 1                | 2                                                     | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 |   |

| A                                                         | В | C | D                | Значения логической функции<br>(для каждого варианта) |   |   |   |   |   |   |   |    |   |

| 0                                                         | 0 | 0 | 0                | 1                                                     | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1  | 0 |

| 0                                                         | 0 | 1 | 0                | 0                                                     | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1  | 1 |

| 0                                                         | 1 | 0 | 0                | 0                                                     | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1  | 0 |

| 0                                                         | 1 | 1 | 0                | 0                                                     | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1  | 0 |

| 1                                                         | 0 | 0 | 0                | 1                                                     | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1  | 0 |

| 1                                                         | 0 | 1 | 0                | 0                                                     | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0  | 0 |

| 1                                                         | 1 | 0 | 0                | 1                                                     | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0  | 0 |

| 1                                                         | 1 | 1 | 0                | 0                                                     | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0  | 0 |

| 0                                                         | 0 | 0 | 1                | 0                                                     | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1  | 1 |

| 0                                                         | 0 | 1 | 1                | 1                                                     | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1  | 1 |

| 0                                                         | 1 | 0 | 1                | 1                                                     | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0  | 1 |

| 0                                                         | 1 | 1 | 1                | 0                                                     | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1 |

| 1                                                         | 0 | 0 | 1                | 1                                                     | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0  | 1 |

| 1                                                         | 0 | 1 | 1                | 0                                                     | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0  | 1 |

| 1                                                         | 1 | 0 | 1                | 1                                                     | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1  | 1 |

| 1                                                         | 1 | 1 | 1                | 1                                                     | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1  | 1 |

<u>Примечание.</u> Значения <u>логических переменных</u>, входящих в вашу логическую функцию, заданы столбцами таблицы (A, B, C, D), они одинаковы для всех вариантов. Из второй части таблицы необходимо выбрать один столбец, согласно вашему варианту, который содержит <u>значения</u> вашей логической функции.

#### 2. Построение структурных схем

По заданной логической функции необходимо построить структурную схему. Варианты логических функций, приведены в таблице 15.

| Вариант | Логическая функция                                                                    |

|---------|---------------------------------------------------------------------------------------|

| 1       | $f = \overline{a \vee b} \wedge c \wedge d \vee e$                                    |

| 2       | $f = \overline{a \wedge c \vee d \vee e \vee b}$                                      |

| 3       | $f = \overline{c \wedge a} \vee b \wedge \overline{d \vee e}$                         |

| 4       | $f = a \lor b \land e \land d \lor c$                                                 |

| 5       | $f = a \lor b \land \overline{c \lor d \lor e}$                                       |

| 6       | $f = a \wedge \overline{c \wedge d} \vee e \vee \overline{b}$                         |

| 7       | $f = \overline{a \lor b} \lor \overline{c \lor d} \land \overline{e}$                 |

| 8       | $f = a \wedge b \wedge \overline{d \vee a} \wedge \overline{e} \vee c$                |

| 9       | $f = \overline{a \wedge a} \wedge \overline{c} \wedge \overline{d} \vee \overline{e}$ |

| 10      | $f = e \lor a \land a \lor d \lor e \land b$                                          |

## 3. Составление логических функций.

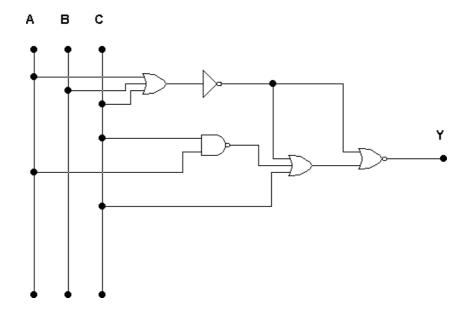

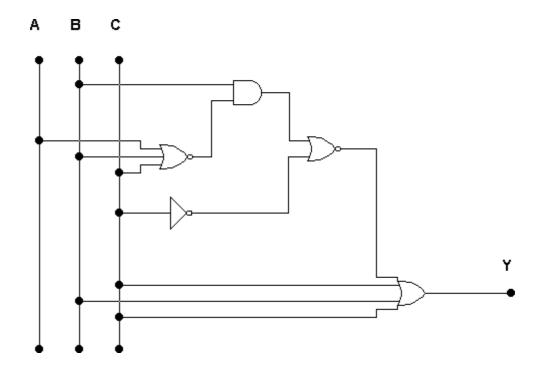

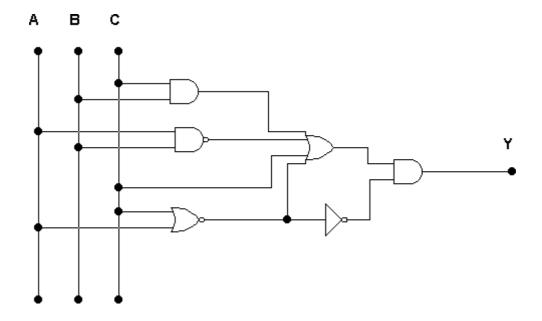

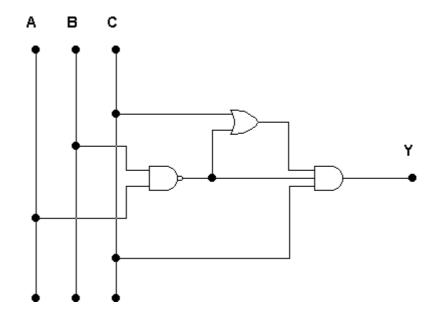

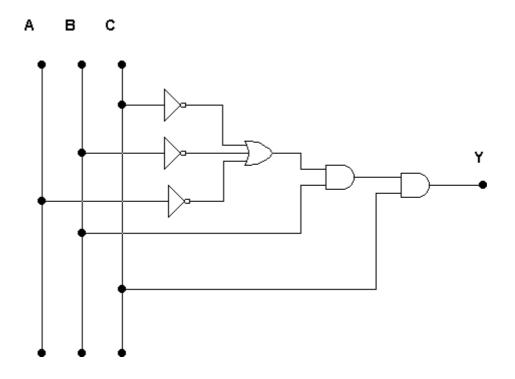

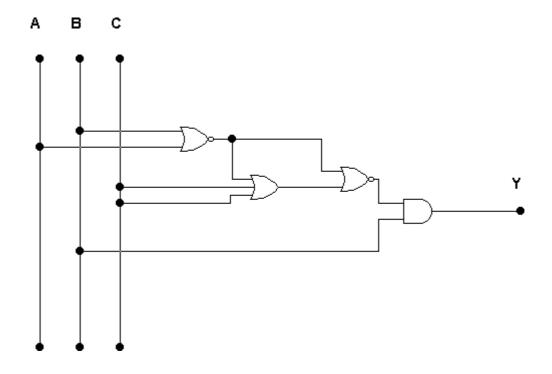

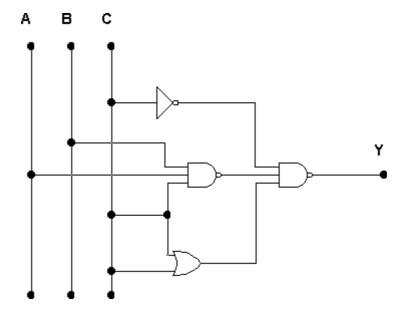

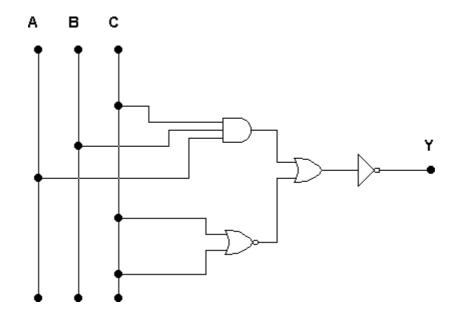

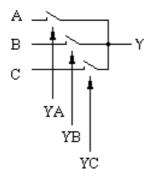

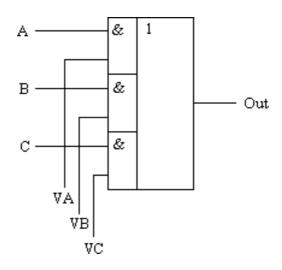

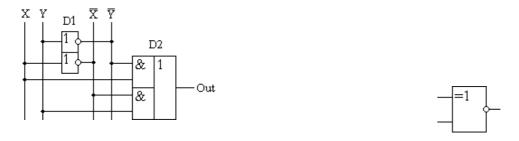

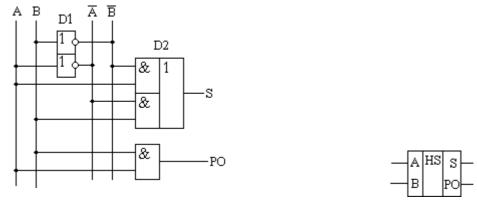

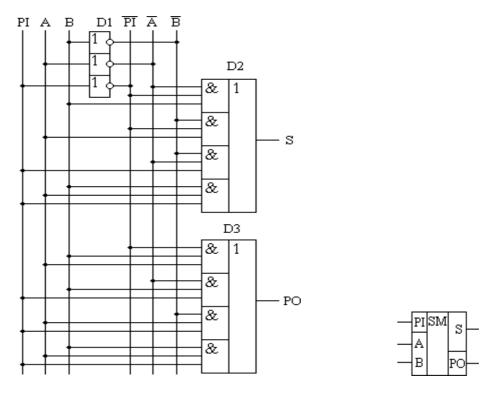

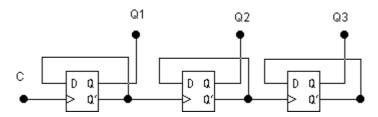

По заданной схеме составьте логическую функцию.

## Вариант 1

Вариант 3

Вариант 4

Вариант 5

## Вариант 6

Вариант 7

Вариант 8

Вариант 9

Вариант 10

#### ЛАБОРАТОРНАЯ РАБОТА № 2

# ИЗУЧЕНИЕ РАБОТЫ ШИФРАТОРОВ, ДЕШИФРАТОРОВ И МУЛЬТИПЛЕКСОРОВ

#### Цель работы.

- 1. Изучение принципов работы шифраторов, дешифраторов и мультиплексоров.

- 2. Реализация логических функций с помощью мультиплексоров.

- 3. Изучение способов применения дешифраторов.

#### Приборы и элементы.

Генератор слов (панель «Instruments/Word Generator»).

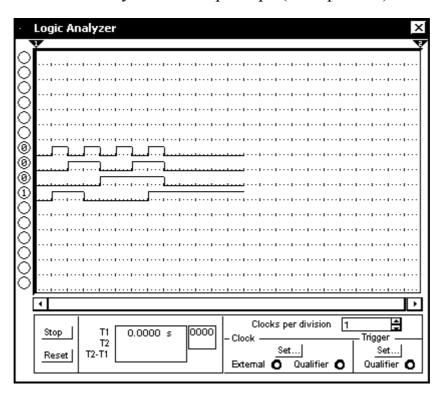

Логический анализатор (панель «Instruments/Logic Analyzer»).

Логические пробники (панель «Indicators/Red probe»).

Источник напряжения + 5 В (панель «Basic/Pull-Up Resistor»).

Земля (панель «Sources/Ground»).

Двухвходовые элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ (панель «Logic Gates/ 2-Input AND, NAND, OR, NOR Gates»).

Двухпозиционные переключатели (панель «Basic/Switch»).

Дешифратор (панель «Digital/DEC/Generic 8-to-1 DEMUX»).

Мультиплексор (панель «Digital/MUX/ Generic 1-of 8 MUX»).

### Краткие теоретические сведения

#### 1. Комбинационные схемы

Комбинационной схемой называется логическая схема, реализующая однозначное соответствие между значениями входных и выходных сигналов. Для реализации комбинационных схем используются логические элементы, выпускаемые в виде интегральных схем. В этот класс входят интегральные схемы дешифраторов, шифраторов, мультиплексоров, демультиплексоров и сумматоров.

### 2. Шифраторы

<u>Шифратор</u> — логическая комбинационная схема, которая имеет  $2^n$  входов (где n — число информационных выходов). Часто n=3, тогда  $2^n$ =8. Подаче на один из входов активного сигнала будет соответствовать двоичное число, которое можно сформировать из его n выходов, эквивалентное номеру входа, на котором появился активный уровень.

<u>Примечание.</u> Формирование двоичного числа на выходе шифратора означает следующее: каждый из выходов шифратора считается определенным разрядом искомого двоичного числа. Принцип работы шифратора противоположен принципу работы дешифратора, который подробно рассмотрен ниже.

Простейшим случаем применения шифратора может служить, например, схема отслеживания нажатия одной кнопки. Каждая кнопка представляет собой элементарный переключатель. Пусть таких кнопок всего 8 и они пронумерованы начиная с «0» и заканчивая «7». При нажатии определенной кнопки (например, «3») формируется сигнал на входе шифратора (каждый вход — это вполне определенная кнопка), в итоге на выходе шифратора можно получить двоичный сигнал, равный номеру нажатой кнопки. В нашем случае число выходов равно 3 ( $2^3$ =8) и на каждом из выходов получится следующая комбинация на 3-м = 0, на 2-м = 1, на 1-м = 1. Полученное двоичное число «011», которое в десятичном коде равно 3.

# 3. Дешифраторы

<u>Дешифратор</u> — логическая комбинационная схема, которая имеет n информационных входов и  $2^n$  выходов. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из  $2^n$  выходов. Обычно n равно 2, 3 или 4. В отечественной литературе входы дешифратора принято обозначать 1, 2, 4, 8, ..., в англоязычной A, B, C, ... Работа дешифратора может быть проиллюстрирована в соответствии с таблицей истинности.

*Таблица 1.* Таблица истинности дешифратора

|   | Bxc | ДЫ |   |   |   |   |   | Вых | оды |   |   |   |   |

|---|-----|----|---|---|---|---|---|-----|-----|---|---|---|---|

| 8 | 4   | 2  | 1 | 0 | 1 | 2 | 3 | 4   | 5   | 6 | 7 | 8 | 9 |

| 0 | 0   | 0  | 0 | 1 | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | 0 |

| 0 | 0   | 0  | 1 | 0 | 1 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | 0 |

| 0 | 0   | 1  | 0 | 0 | 0 | 1 | 0 | 0   | 0   | 0 | 0 | 0 | 0 |

| 0 | 0   | 1  | 1 | 0 | 0 | 0 | 1 | 0   | 0   | 0 | 0 | 0 | 0 |

| 0 | 1   | 0  | 0 | 0 | 0 | 0 | 0 | 1   | 0   | 0 | 0 | 0 | 0 |

| 0 | 1   | 0  | 1 | 0 | 0 | 0 | 0 | 0   | 1   | 0 | 0 | 0 | 0 |

| 0 | 1   | 1  | 0 | 0 | 0 | 0 | 0 | 0   | 0   | 1 | 0 | 0 | 0 |

| 0 | 1   | 1  | 1 | 0 | 0 | 0 | 0 | 0   | 0   | 0 | 1 | 0 | 0 |

| 1 | 0   | 0  | 0 | 0 | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 1 | 0 |

| 1 | 0   | 0  | 1 | 0 | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | 1 |

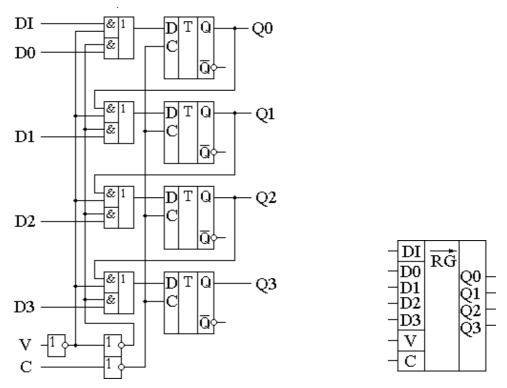

На рис. 1 представлен дешифратор, имеющий таблицу истинности табл. 1. Условное обозначение базовых элементов соответствует обозначению, принятому в отечественной литературе.

В дальнейшем для детального рассмотрения дешифратора мы будем пользоваться обозначениями (микросхем и базовых элементов), принятыми в EWB. На рис. 2 изображен дешифратор (блок микросхемы, использующийся для моделирования дешифратора в EWB) с n = 3.

Активным уровнем сигнала данной микросхемы является уровень логического нуля, т.е. в отличие от таблицы истинности 1 у данного дешифратора на выходах по диагонали расположены нули, а остальные элементы равны единице. На входы C, B, A можно подать следующие комбинации логических уровней: «000», «001», «010», …, «111», всего 8 комбинаций. Схема имеет 8 выходов, на одном из которых формируется низкий потенциал, на остальных — высокий. Номер этого единственного выхода, на котором формируется активный (нулевой) уровень, соответствует числу N, определяемому состоянием входов C, B, A следующим образом:

$$N = C \cdot 2^2 + B \cdot 2^1 + A \cdot 2^0 \tag{1}$$

Например, если на входы подана комбинация логических уровней «011», то из 8 выходов микросхемы на выходе с номером N=3 (в двоичном

исчислении 3 = 011) установится нулевой уровень сигнала (Y3=0), а все остальные выходы будут иметь уровень логической единицы. Этот принцип формирования выходного сигнала можно описать следующим образом:

$$Y = \begin{cases} 0, \text{ если } i = k \\ \neq k, \end{cases}$$

(2)

$$\{1, \text{ если i} \ | \ \mathbf{k} = 2^2 \cdot C + 2^1 \cdot B + 2^0 \cdot A.$$

Помимо информационных входов A,B,C, дешифраторы обычно имеют дополнительные входы управления G. Сигналы на этих входах, например, разрешают функционирование дешифратора или переводят его в пассивное состояние, при котором (независимо от сигналов на информационных входах) на всех выходах установится уровень логической единицы. Можно сказать, что существует некоторая функция разрешения, значение которой определяется состояниями управляющих входов.

Разрешающий вход дешифратора может быть прямым или инверсным. У дешифраторов с прямым разрешающим входом активным уровнем является уровень логической единицы, у дешифраторов с инверсным входом — уровень логического нуля. На рис. 2 представлен дешифратор с одним инверсным входом управления. Принцип формирования выходного сигнала в этом дешифраторе с учетом сигнала управления описывается следующим образом:

$$Y_{i} = \begin{cases} 1 \cdot G, \text{ если } i = k, \\ 1, \text{ если } i \neq k, \\ k = 2^{2} \cdot C + 2^{1} \cdot B + 2^{0} \cdot A. \end{cases}$$

$$(3)$$

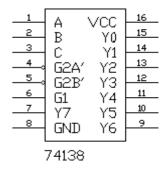

У дешифратора с несколькими входами управления функция разрешения, как правило, представляет собой логическое произведение всех разрешающих сигналов управления. Например, для дешифратора серии 74138 с одним прямым входом управления G1 и двумя инверсными G2A и G2B (рис. 3) функции выхода  $Y_i$  и разрешения G имеют вид:

*Рис. 3.* Дешифратор серии 74138.

$$Y_{i} = \begin{cases} 1 \cdot G, \text{ если } i = k, \\ 1, \text{ если } i \neq k, \\ k = 2^{2} \cdot C + 2^{1} \cdot B + 2^{0} \cdot A. \end{cases}$$

$$(4)$$

$$G = G1 \cdot \overline{G2} A \cdot \overline{G2}B \tag{5}$$

Обычно входы управления используются для каскадирования (увеличения разрядности) дешифраторов или при параллельной работе нескольких схем на общие выходные линии.

Дешифратор может быть использован как демультиплексор — логический коммутатор, подключающий входной сигнал к одному из выходов. В этом случае функцию информационного входа выполняет один из входов разрешения, а состояние входов C, B и A задает номер выхода, на который передается сигнал с входа разрешения.

#### 4. Мультиплексоры

<u>Мультиплексор</u> — комбинационная логическая схема, представляющая собой управляемый переключатель, который подключает к выходу один из входов данных. Номер подключаемого входа равен числу (адресу), определяемому комбинацией логических уровней на адресных входах.

<u>Демультиплексорами</u> называются устройства, которые позволяют подключать один вход к нескольким выходам.

В простейшем случае переключения (коммутацию) можно осуществить при помощи ключей, как это показано на рис. 4.

Рис. 4. Мультиплексор на ключах.

В цифровых схемах управление ключами осуществляется при помощи логических сигналов. Сами ключи при этом заменяются соответствующими логическим элементами.

Рассмотрим пример простейшей схемы мультиплексора. Для этого воспользуемся базовым логическим элементом «И» с таблицей истинности 2.

Теперь один из входов элемента будем рассматривать как информацион-

ный вход электронного ключа, а другой — как адресный. По таблице истинности отчетливо видно, что пока на адресный вход Y подан логический уровень «0» сигнал с входа X на выход Out не проходит.

*Таблица 2*. Таблица истинности элемента «И»

| Bx | оды | Выход |

|----|-----|-------|

| X  | Y   | Out   |

| 0  | 0   | 0     |

| 0  | 1   | 0     |

| 1  | 0   | 0     |

| 1  | 1   | 1     |

При подаче на адресный вход Y логической «1» сигнал, поступающий на вход X, поступает на выход Out, т.е. логический элемент «И» можно использовать в качестве электронного ключа. При этом неважно, какой из входов элемента будет использоваться в качестве адресного входа, а какой — в качестве информационного. Остается только объединить выходы элементов «И» на один выход. Это делается при помощи элемента «ИЛИ». Условное обозначение такой схемы приведено на рис. 5.

*Рис.* 5. Принципиальная схема мультиплексора.

Чаще всего для управления требуется много входов, поэтому в схему мультиплексора включают дешифратор. Это позволяет управлять переключе- нием входов микросхемы на выход при помощи двоичных кодов.

Для дальнейшего рассмотрения мультиплексоров мы будем как и прежде пользоваться условными обозначениями логических элементов и микросхем, принятых в EWB.

Кроме информационных и адресных входов, схемы мультиплексоров содержат вход разрешения, при подаче на который активного уровня мультиплексор переходит в рабочее состояние. При подаче на вход разрешения пассивного уровня мультиплексор перейдет в нерабочее состояние, в котором сигнал на выходе сохраняет постоянное значение независимо от значений ин-

формационных и управляющих сигналов. Число информационных входов у мультиплексоров обычно равно 2, 4, 8 или 16.

На рис. 7 представлен мультиплексор (блок микросхемы, использующийся для моделирования дешифратора в EWB) 8х1 с инверсным входом разрешения G, прямым Y и инверсным W-выходами ( $W = \overline{Y}$ )

*Puc. 7.* Мультиплексор.

#### 5. Реализация логических функций

Функционирование мультиплексора, представленного на рис. 7, описывается характеристическим уравнением, связывающим сигнал на выходе (Y) с разрешающим (G), входными информационными (DO...D7) и адресными (A, B, C) сигналами:

$$\left[ + C \cdot B \cdot A \cdot D4 + C \cdot B \cdot A \cdot D5 + C \cdot B \cdot A \cdot D6 + C \cdot B \cdot A \cdot D7 \right]$$

Как видно из уравнения, на мультиплексоре можно реализовать логические функции, для чего нужно определить, какие сигналы и логические константы следует подавать на входы мультиплексора.

Логическая функция n переменных определена для  $2^n$  комбинаций значений переменных. Это позволяет реализовать функцию n переменных на мультиплексоре, имеющем n адресных и  $2^n$  информационных входов. В этом случае каждой комбинации значений аргументов соответствует единственный информационный вход мультиплексора, на который подается значение функции.

Например, требуется реализовать функцию:

$$F_1 = \overline{c} \cdot \overline{b} \cdot \overline{a} \vee c \cdot b \cdot a \vee c \cdot b \cdot \overline{a} \vee \overline{c} \cdot b \cdot a . \tag{7}$$

Эта функция определена только для 8 комбинаций значений переменных, поэтому для ее реализации можно использовать мультиплексор 8x1 с тремя адресными входами. Составим таблицу истинности функции (табл. 3).

Tаблица 3. Таблица истинности логической функции  $F_1$

| Вход           | Лог | ические перемен | ные | Выход          |

|----------------|-----|-----------------|-----|----------------|

| мультиплексора |     |                 |     | функции        |

| N              | С   | b               | a   | $\mathbf{F_1}$ |

| 0              | 0   | 0               | 0   | 1              |

| 1              | 0   | 0               | 1   | 0              |

| 2              | 0   | 1               | 0   | 0              |

| 3              | 0   | 1               | 1   | 1              |

| 4              | 1   | 0               | 0   | 0              |

| 5              | 1   | 0               | 1   | 0              |

| 6              | 1   | 1               | 0   | 1              |

| 7              | 1   | 1               | 1   | 1              |

Из табл. З видно, что для реализации функции на мультиплексоре необходимо подать на информационный вход мультиплексора с номером N сигнал, значение которого равно соответствующему значению функции  $F_I$ , т.е. на входы с номерами 1, 2, 4, 5 следует подать уровень логического нуля, а на остальные — уровень логической единицы. Таким образом, при подаче комби-

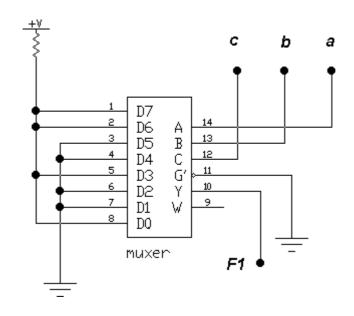

нации логических уровней (a, b, c) на адресные входы мультиплексора к его выходу подключится вход, значение сигнала на котором равно соответствующему значению функции. Схемная реализация приведена на рис. 8.

Рис. 8. Реализация логической функции.

При реализации логических функций на информационные входы можно подавать не только константы, но и изменяющиеся входные сигналы. Рассмотрим, например, другой способ реализации функции  $F_I$ , определенной выражением (7). Для этого минимизируем выражение функции с помощью известных логических тождеств (см. лабораторную работу  $\mathbb{N}$  1) до вида:

$$F_1 = \overline{c} \cdot \overline{b} \cdot \overline{a} \vee b \cdot c \vee b \cdot a. \tag{8}$$

Составим таблицу истинности функции (8) в зависимости от значений переменных a и b (см. табл. 4).

Для составления таблицы в выражение (8) подставляли комбинации a и b и, пользуясь логическим тождествами (см. лабораторную работу № 1), получали значение функции  $F_I$ . Заданную такой таблицей функцию реализуют, как и в предыдущем случае, подав на вход с номером N сигнал, значение которого соответствует значению функции  $F_I$ .

Tаблица 4. Таблица истинности упрощенной логической функции  $F_I$

| Вход           | Логические | Логические переменные |                |  |  |  |  |  |

|----------------|------------|-----------------------|----------------|--|--|--|--|--|

| мультиплексора |            |                       | функции        |  |  |  |  |  |

| N              | b          | a                     | F <sub>1</sub> |  |  |  |  |  |

| 0 | 0 | 0 | С |

|---|---|---|---|

| 1 | 0 | 1 | 0 |

| 2 | 1 | 0 | С |

| 3 | 1 | 1 | 1 |

В данном случае сигналы c и  $\overline{c}$ , соответствующие переменной c, подаются на информационные входы, как указано в таблице истинности. При этом сокращается число управляющих входов.

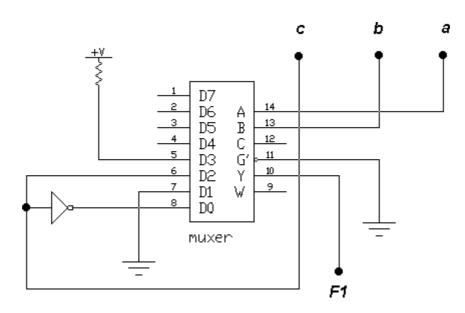

Схемная реализация такого способа задания функции приведена на рис. 9.

Рис. 9. Реализация упрощенной логической функции.

Так как используются только два адресных входа, вход C остается неподключенным. При этом состояние информационных входов D4...D7 безразлично. Схема рис. 9 по существу представляет собой мультиплексор 4x1 с 2 адресными и 4 информационными входами.

Если функцию можно представить в виде произведения одночлена на многочлен, то ее также можно реализовать при помощи мультиплексора. Как следует из уравнения мультиплексора, сигнал, соответствующий одночлену, нужно подать на вход разрешения. Например, требуется реализовать функцию  $F_2$ , описываемую следующим выражением:

$$F_2 = \overline{x} \cdot (d \cdot c \cdot \overline{b} \vee d \cdot \overline{b} \cdot a \vee e \cdot \overline{c} \cdot b \cdot a \vee c \cdot b \cdot a). \tag{9}$$

При реализации данной функции на мультиплексоре сигнал, соответ-

ствующий переменной x, следует подать на его разрешающий вход. Рассмотрим, какие сигналы необходимо подать на управляющие входы мультиплексора. Выражение в скобках можно рассматривать как некоторую функцию f пяти переменных: a, b, c, d, e, из которых наиболее часто используются переменные a, b и c. Поэтому сигналы, соответствующие этим переменным, нужно подать на адресные входы мультиплексора.

Определим, какие сигналы следует подать на информационные входы, чтобы реализовать функцию f. Для этого составим таблицу истинности функции в зависимости от значений переменных a, b и c (табл. 5).

Tаблица 5. Таблица истинности логической функции  $F_2$

| Вход           | Лог | ические перемен | ные | Выход   |

|----------------|-----|-----------------|-----|---------|

| мультиплексора |     |                 |     | функции |

| N              | с   | b               | a   | f       |

| 0              | 0   | 0               | 0   | 0       |

| 1              | 0   | 0               | 1   | d       |

| 2              | 0   | 1               | 0   | 0       |

| 3              | 0   | 1               | 1   | е       |

| 4              | 1   | 0               | 0   | d       |

| 5              | 1   | 0               | 1   | d       |

| 6              | 1   | 1               | 0   | 0       |

| 7              | 1   | 1               | 1   | 1       |

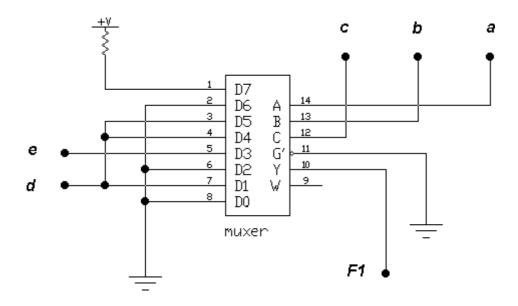

Из табл. 5 видно, что на информационные входы с номерами  $N=0,\,2,\,6$  нужно подать уровень логического нуля. Сигнал, соответствующий переменной d, нужно подать на входы с номерами  $N=1,\,4,\,5,\,$  сигнал, соответствующий переменной e, — на вход с номером 3. Схемная реализация такого способа задания функции приведена на рис. 10.

*Puc. 10.* Реализация логической функции  $F_2$ .

#### Порядок работы

#### Задание 1. Исследование работы шифратора

Создайте схему, изображенную на рис. 11. Над генератором слов написаны цифры от 0 до 7 — они обозначают номера входов шифратора, на которые соответственно подаются сигналы управления. Сам шифратор составлен из трех элементов «ИЛИ». Выходы шифратора обозначаются как A, B, C, где A — старший бит, B — средний бит, а C — младший бит двоичного числа, получаемого на выходе. (Это число показывает, на какой из входов подан логический сигнал).

Запрограммируйте генератор слов так, чтобы на его выходах сформировалась двоичная последовательность, эмулирующая поочередную подачу на вход шифратора сигнала логической единицы. Пошагово изменяя значения входов дешифратора (кнопкой «Step» в генераторе слов), заполните таблицу истинности шифратора (табл. 6).

*Таблица 6*. Таблица истинности шифратора

|   | Входы шифратора |   |   |   |   |   |   |     | Выходы шифратора |            |  |  |  |  |  |

|---|-----------------|---|---|---|---|---|---|-----|------------------|------------|--|--|--|--|--|

|   |                 |   |   |   |   |   |   | Дво | ичное чи         | Десятичное |  |  |  |  |  |

| 0 | 1               | 2 | 3 | 4 | 5 | 6 | 7 | C   | В                | число      |  |  |  |  |  |

| 0 | 0               | 0 | 0 | 0 | 0 | 0 | 0 |     |                  |            |  |  |  |  |  |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

|---|---|---|---|---|---|---|---|--|--|

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |  |  |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |  |  |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |  |  |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |  |  |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |  |  |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |  |  |

Переведите полученное двоичное число, составленное из разрядов CBA, в десятичное. Сделайте вывод о работе шифратора.

# Задание 2. Исследование работы дешифраторов

Исследование развернутой схемы дешифратора.

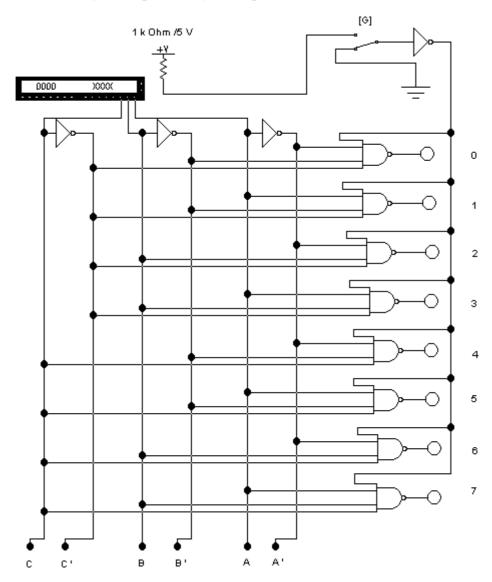

Создайте схему изображенную на рис. 12.

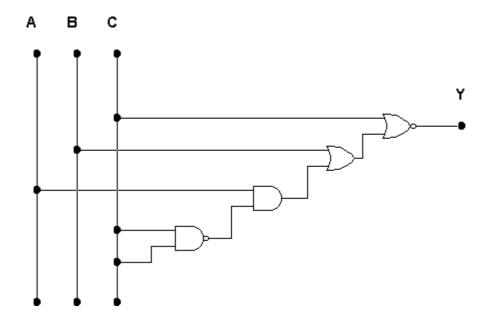

Рис. 12. Развернутая схема дешифратора.

Здесь представлен дешифратор 3\*8 (3 входа, 8 выходов). Он составлен из элементов «И-НЕ». C, B, A — входы дешифратора, 0, 1, ..., 7 — выходы, G —

вход разрешения.

Запрограммируйте генератор слов так, чтобы на его выходе сформировать все возможные комбинации трехразрядного двоичного числа. Подавая на вход дешифратора различные комбинации двоичного числа C, B, A (кнопкой «Step» в генераторе слов) и разрешения G (ключом G), заполните таблицу истинности дешифратора (табл. 7).

Таблица 7.

Таблица истинности развернутой схемы дешифратора

| E     | Входы д | цешифј | ратора |   |   |   | Вых | оды де | шифра | тора |   |   |

|-------|---------|--------|--------|---|---|---|-----|--------|-------|------|---|---|

| Число | C       | В      | A      | G | 0 | 1 | 2   | 3      | 4     | 5    | 6 | 7 |

| 0     | 0       | 0      | 0      | 0 |   |   |     |        |       |      |   |   |

| 1     | 0       | 0      | 1      | 0 |   |   |     |        |       |      |   |   |

| 2     | 0       | 1      | 0      | 0 |   |   |     |        |       |      |   |   |

| 3     | 0       | 1      | 1      | 0 |   |   |     |        |       |      |   |   |

| 4     | 1       | 0      | 0      | 0 |   |   |     |        |       |      |   |   |

| 5     | 1       | 0      | 1      | 0 |   |   |     |        |       |      |   |   |

| 6     | 1       | 1      | 0      | 0 |   |   |     |        |       |      |   |   |

| 7     | 1       | 1      | 1      | 0 |   |   |     |        |       |      |   |   |

| 0     | 0       | 0      | 0      | 1 |   |   |     |        |       |      |   |   |

| 1     | 0       | 0      | 1      | 1 |   |   |     |        |       |      |   |   |

| 2     | 0       | 1      | 0      | 1 |   |   |     |        |       |      |   |   |

| 3     | 0       | 1      | 1      | 1 |   |   |     |        |       |      |   |   |

| 4     | 1       | 0      | 0      | 1 |   |   |     |        |       |      |   |   |

| 5     | 1       | 0      | 1      | 1 |   |   |     |        |       |      |   |   |

| 6     | 1       | 1      | 0      | 1 |   |   |     |        |       |      |   |   |

| 7     | 1       | 1      | 1      | 1 |   |   |     |        |       |      |   |   |

Сделайте вывод о работе дешифратора.

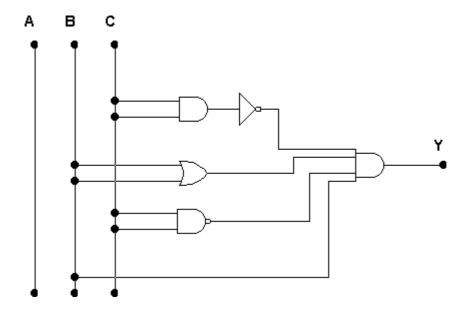

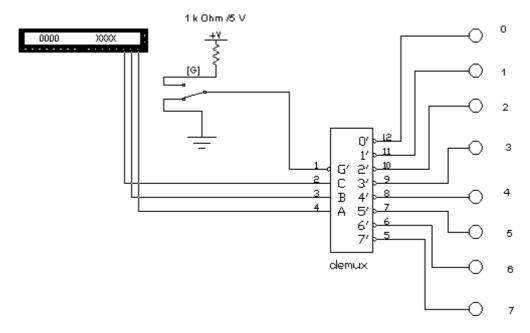

*Исследование работы схемы дешифратора 3\*8 в основном режиме.* Создайте схему, изображенную на рис. 13.

Рис. 13. Схема дешифратора.

Запрограммируйте генератор слов аналогично предыдущему пункту. Подавая на вход дешифратора различные комбинации двоичного числа C, B, A (кнопкой «Step» в генераторе слов) и разрешения G (ключом G), заполните таблицу истинности дешифратора (данная таблица составляется аналогично табл. 7).

Сделайте вывод о работе дешифратора. Сравните полученную в данном пункте таблицу с табл. 7.

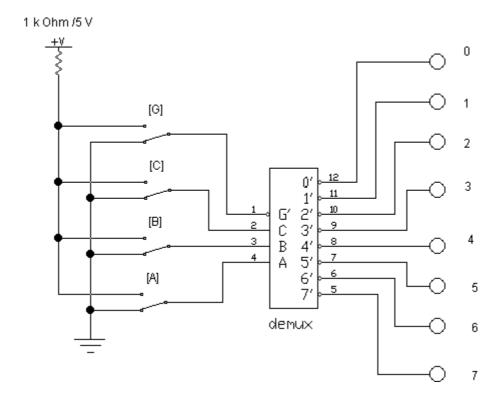

*Исследование работы схемы дешифратора 3\*8 в режиме2\*4*. Создайте схему, изображенную на рис. 14.

Рис. 14. Дешифратор в режиме 2\*4.

В этой схеме подключите вход C к общему проводу (земле), задав C=0. Изменяя сигналы на входах B и A, пронаблюдайте уровни сигналов на выходах схемы (с помощью логических пробников, установленных на выходах). Укажите выходы, на которых уровень сигнала не меняется.

Подключите вход C к источнику питания (логической единице), задав C=1. Аналогично изменяя сигналы на входах B и A, пронаблюдайте уровни сигналов на выходах схемы (с помощью логических пробников, установленных на выходах). Укажите выходы, на которых уровень сигнала не меняется.

Заземлите вход B (B=0), подавая на входы A и C все возможные комбинации логических уровней, сделайте вывод о работе схемы в этом случае.

Сформулируйте принцип, по которому можно использовать дешифраторы на меньшую разрешающую способность, чем та, на которую он рассчитан.

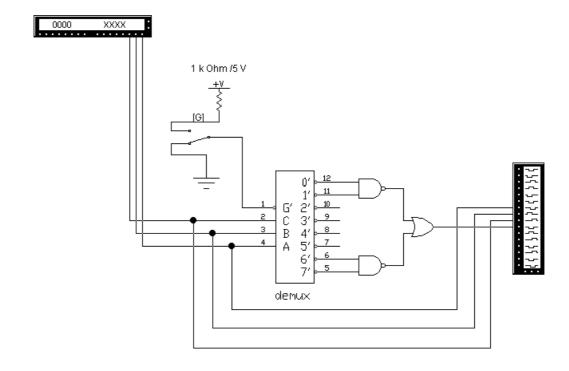

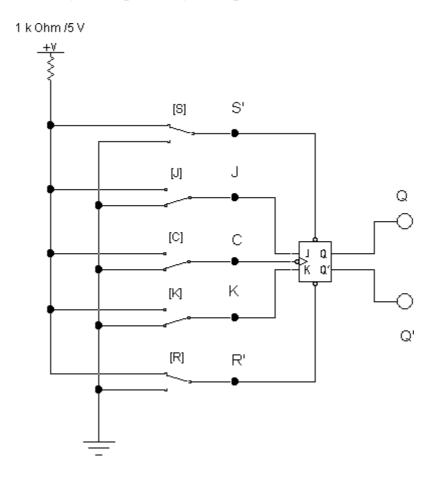

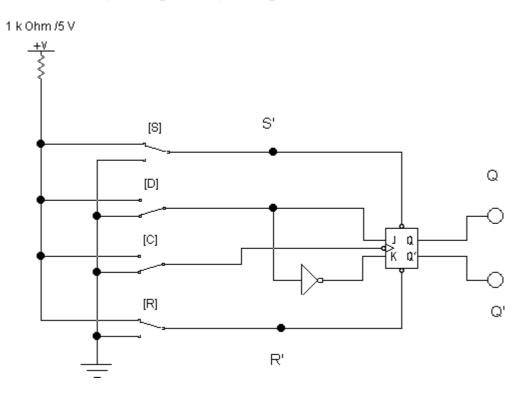

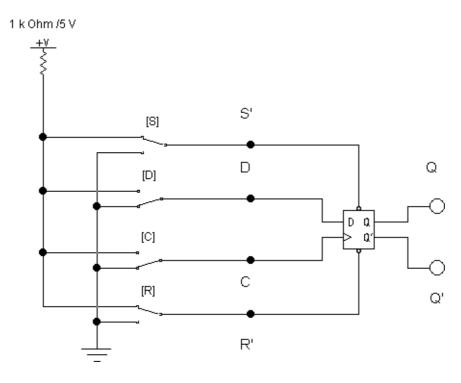

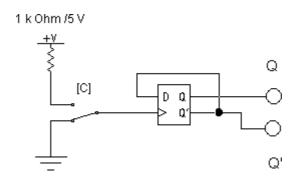

#### Задание 3. Применение дешифраторов